Phần tử hoạt động quang tử silicon

Các linh kiện hoạt động trong quang học đề cập cụ thể đến các tương tác động được thiết kế có chủ đích giữa ánh sáng và vật chất. Một linh kiện hoạt động điển hình của quang học là bộ điều biến quang học. Tất cả các thiết bị dựa trên silicon hiện naybộ điều biến quang họcdựa trên hiệu ứng chất mang tự do plasma. Việc thay đổi số lượng electron và lỗ trống tự do trong vật liệu silicon bằng cách pha tạp, các phương pháp điện hoặc quang học có thể thay đổi chỉ số khúc xạ phức của nó, một quá trình được thể hiện trong các phương trình (1,2) thu được bằng cách khớp dữ liệu từ Soref và Bennett ở bước sóng 1550 nanomet. So với electron, lỗ trống gây ra tỷ lệ thay đổi chỉ số khúc xạ thực và ảo lớn hơn, nghĩa là chúng có thể tạo ra sự thay đổi pha lớn hơn cho một sự thay đổi tổn hao nhất định, vì vậy trongBộ điều biến Mach-Zehndervà bộ điều biến vòng, người ta thường ưu tiên sử dụng các lỗ để tạo rabộ điều biến pha.

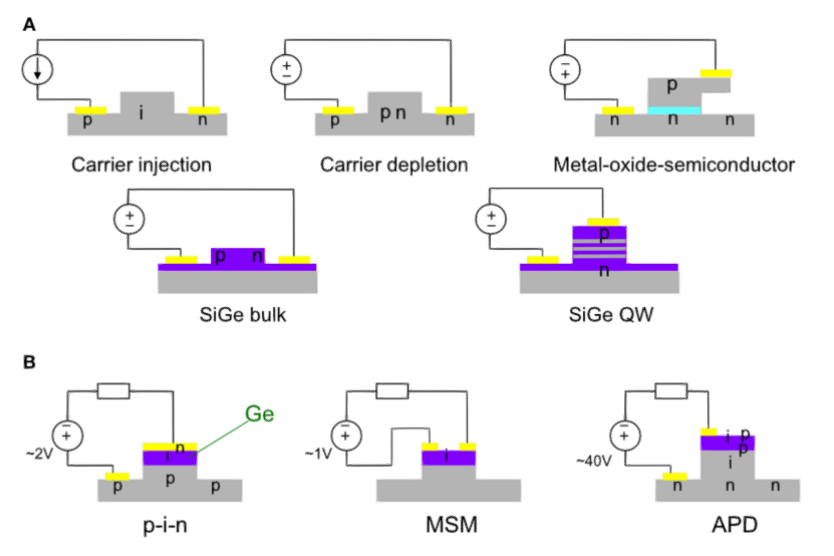

Các loại khác nhaubộ điều biến silicon (Si)Các loại được thể hiện trong Hình 10A. Trong bộ điều biến tiêm chất mang, ánh sáng nằm trong silicon nội tại bên trong một mối nối pn rất rộng, và các electron và lỗ trống được tiêm vào. Tuy nhiên, các bộ điều biến như vậy chậm hơn, thường có băng thông 500 MHz, vì các electron và lỗ trống tự do cần nhiều thời gian hơn để tái kết hợp sau khi tiêm. Do đó, cấu trúc này thường được sử dụng như một bộ suy giảm quang học biến đổi (VOA) hơn là một bộ điều biến. Trong bộ điều biến suy giảm chất mang, phần ánh sáng nằm trong một mối nối pn hẹp, và chiều rộng vùng suy giảm của mối nối pn được thay đổi bằng điện trường đặt vào. Bộ điều biến này có thể hoạt động ở tốc độ vượt quá 50 Gb/s, nhưng có tổn hao chèn nền cao. Điện áp đỉnh (vpil) điển hình là 2 V-cm. Bộ điều biến bán dẫn oxit kim loại (MOS) (thực chất là bán dẫn-oxit-bán dẫn) chứa một lớp oxit mỏng trong mối nối pn. Nó cho phép tích tụ cũng như suy giảm điện tích, cho phép VπL nhỏ hơn, khoảng 0,2 V-cm, nhưng có nhược điểm là tổn hao quang học cao hơn và điện dung trên mỗi đơn vị chiều dài cao hơn. Ngoài ra, còn có các bộ điều biến hấp thụ điện SiGe dựa trên sự dịch chuyển biên dải SiGe (hợp kim silicon-germanium). Thêm vào đó, có các bộ điều biến graphene dựa vào graphene để chuyển đổi giữa các kim loại hấp thụ và chất cách điện trong suốt. Điều này cho thấy sự đa dạng trong ứng dụng của các cơ chế khác nhau để đạt được điều biến tín hiệu quang tốc độ cao, tổn hao thấp.

Hình 10: (A) Sơ đồ mặt cắt ngang của các thiết kế bộ điều biến quang dựa trên silicon khác nhau và (B) sơ đồ mặt cắt ngang của các thiết kế bộ dò quang.

Hình 10B hiển thị một số bộ детектор ánh sáng dựa trên silicon. Vật liệu hấp thụ là germanium (Ge). Ge có khả năng hấp thụ ánh sáng ở bước sóng xuống đến khoảng 1,6 micromet. Hình bên trái là cấu trúc chân cắm thành công nhất về mặt thương mại hiện nay. Nó bao gồm silicon pha tạp loại P, trên đó Ge được phát triển. Ge và Si có độ lệch mạng tinh thể 4%, và để giảm thiểu sự sai lệch, một lớp mỏng SiGe được phát triển trước tiên như một lớp đệm. Việc pha tạp loại N được thực hiện trên lớp Ge. Một điốt quang kim loại-bán dẫn-kim loại (MSM) được hiển thị ở giữa, và một APD (Bộ tách sóng quang avalancheHình (được hiển thị ở bên phải). Vùng thác lũ trong APD nằm trong Si, có đặc tính nhiễu thấp hơn so với vùng thác lũ trong các vật liệu nguyên tố nhóm III-V.

Hiện tại, chưa có giải pháp nào có ưu điểm rõ rệt trong việc tích hợp khuếch đại quang học với quang tử silicon. Hình 11 trình bày một số tùy chọn khả thi được sắp xếp theo cấp độ lắp ráp. Ở cột ngoài cùng bên trái là các tích hợp nguyên khối bao gồm việc sử dụng germanium (Ge) được nuôi cấy bằng phương pháp epitaxy làm vật liệu khuếch đại quang học, ống dẫn sóng thủy tinh pha tạp erbium (Er) (như Al2O3, cần bơm quang học) và chấm lượng tử gallium arsenide (GaAs) được nuôi cấy bằng phương pháp epitaxy. Cột tiếp theo là lắp ráp từ wafer này sang wafer khác, liên quan đến liên kết oxit và hữu cơ trong vùng khuếch đại nhóm III-V. Cột tiếp theo là lắp ráp từ chip sang wafer, bao gồm việc nhúng chip nhóm III-V vào khoang của wafer silicon và sau đó gia công cấu trúc ống dẫn sóng. Ưu điểm của phương pháp ba cột đầu tiên là thiết bị có thể được kiểm tra đầy đủ chức năng bên trong wafer trước khi cắt. Cột ngoài cùng bên phải là lắp ráp từ chip sang chip, bao gồm ghép nối trực tiếp các chip silicon với các chip nhóm III-V, cũng như ghép nối thông qua thấu kính và bộ ghép nối lưới. Xu hướng ứng dụng thương mại đang dịch chuyển từ bên phải sang bên trái của biểu đồ, hướng tới các giải pháp tích hợp và toàn diện hơn.

Hình 11: Cách tích hợp độ khuếch đại quang học vào quang tử dựa trên silicon. Khi di chuyển từ trái sang phải, điểm chèn trong quá trình sản xuất dần dần dịch chuyển về phía sau.

Thời gian đăng bài: 22/7/2024