Sử dụngquang điện tửCông nghệ đóng gói chung để giải quyết vấn đề truyền tải dữ liệu khổng lồ.

Được thúc đẩy bởi sự phát triển mạnh mẽ của sức mạnh tính toán, lượng dữ liệu đang tăng lên nhanh chóng, đặc biệt là lưu lượng truy cập kinh doanh trung tâm dữ liệu mới như các mô hình AI quy mô lớn và máy học đang thúc đẩy sự tăng trưởng dữ liệu từ đầu đến cuối và đến người dùng. Lượng dữ liệu khổng lồ cần được truyền tải nhanh chóng đến mọi hướng, và tốc độ truyền dữ liệu cũng đã phát triển từ 100GbE lên 400GbE, hoặc thậm chí 800GbE, để đáp ứng nhu cầu về sức mạnh tính toán và tương tác dữ liệu ngày càng tăng. Khi tốc độ đường truyền tăng lên, độ phức tạp ở cấp độ bo mạch của phần cứng liên quan đã tăng lên đáng kể, và I/O truyền thống không thể đáp ứng được các yêu cầu khác nhau của việc truyền tín hiệu tốc độ cao từ ASIC đến bảng điều khiển phía trước. Trong bối cảnh này, việc đóng gói quang điện tử CPO đang được tìm kiếm.

Nhu cầu xử lý dữ liệu tăng đột biến, CPOquang điện tửsự chú ý của đồng niêm phong

Trong hệ thống truyền thông quang học, mô-đun quang học và chip chuyển mạch mạng (AISC) được đóng gói riêng biệt, vàmô-đun quang họcNó được cắm vào bảng điều khiển phía trước của bộ chuyển mạch ở chế độ cắm. Chế độ cắm không còn xa lạ, và nhiều kết nối I/O truyền thống được kết nối với nhau ở chế độ này. Mặc dù cắm vẫn là lựa chọn hàng đầu về mặt kỹ thuật, nhưng chế độ cắm đã bộc lộ một số vấn đề ở tốc độ dữ liệu cao, và chiều dài kết nối giữa thiết bị quang học và bảng mạch, tổn hao truyền tín hiệu, mức tiêu thụ điện năng và chất lượng sẽ bị hạn chế khi tốc độ xử lý dữ liệu cần tăng lên hơn nữa.

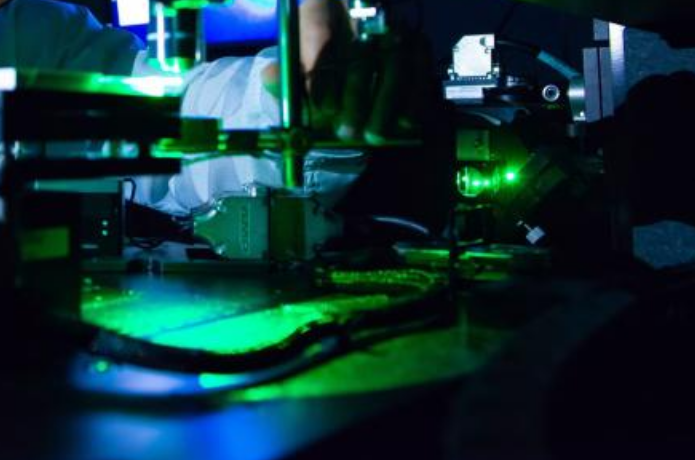

Để giải quyết những hạn chế của kết nối truyền thống, công nghệ đóng gói quang điện tử CPO đang bắt đầu nhận được sự chú ý. Trong quang học đóng gói đồng thời, các mô-đun quang học và chip chuyển mạch mạng (AISC) được đóng gói cùng nhau và kết nối thông qua các kết nối điện ngắn, từ đó đạt được sự tích hợp quang điện tử nhỏ gọn. Ưu điểm về kích thước và trọng lượng do đóng gói quang điện tử CPO mang lại là rõ ràng, và việc thu nhỏ và tối ưu hóa các mô-đun quang tốc độ cao được thực hiện. Mô-đun quang học và chip chuyển mạch mạng (AISC) được tập trung hơn trên bo mạch, và chiều dài sợi quang có thể được giảm đáng kể, điều này có nghĩa là tổn thất trong quá trình truyền dẫn có thể được giảm thiểu.

Theo dữ liệu thử nghiệm của Ayar Labs, việc đóng gói quang học CPO thậm chí có thể giảm trực tiếp mức tiêu thụ điện năng xuống một nửa so với các mô-đun quang cắm truyền thống. Theo tính toán của Broadcom, trên mô-đun quang cắm 400G, phương án CPO có thể tiết kiệm khoảng 50% điện năng tiêu thụ, và so với mô-đun quang cắm 1600G, phương án CPO tiết kiệm được nhiều điện năng hơn. Bố cục tập trung hơn cũng giúp tăng đáng kể mật độ kết nối, cải thiện độ trễ và méo tín hiệu điện, đồng thời loại bỏ hạn chế về tốc độ truyền tải như ở chế độ cắm truyền thống.

Một điểm quan trọng khác là chi phí. Ngày nay, trí tuệ nhân tạo, hệ thống máy chủ và chuyển mạch đòi hỏi mật độ và tốc độ cực cao, nhu cầu hiện tại đang tăng nhanh. Nếu không sử dụng công nghệ đóng gói chung CPO, sẽ cần một lượng lớn các đầu nối cao cấp để kết nối mô-đun quang, điều này gây ra chi phí rất lớn. Việc đóng gói chung CPO có thể giảm số lượng đầu nối, góp phần lớn vào việc giảm chi phí linh kiện (BOM). Đóng gói chung các linh kiện quang điện CPO là cách duy nhất để đạt được mạng tốc độ cao, băng thông rộng và công suất thấp. Công nghệ đóng gói các linh kiện quang điện silicon và linh kiện điện tử này giúp mô-đun quang càng gần chip chuyển mạch mạng càng tốt, giảm tổn hao kênh và gián đoạn trở kháng, cải thiện đáng kể mật độ kết nối và cung cấp hỗ trợ kỹ thuật cho kết nối dữ liệu tốc độ cao hơn trong tương lai.

Thời gian đăng bài: 01/04/2024